# MICROPROCESSOR ARCHITECTURE

UOP S.E.COMP (SEM-I)

# 8086 MICROPROCESSOR ARCHITECTURE

#### Prof.P.C.Patil

**Department of Computer Engg Matoshri College of Engg.Nasik**

pcpatil18@gmail.com.

# 8086 Programmers Model

# 8086 Programmers Model

|               |    |          |    | 1                          |

|---------------|----|----------|----|----------------------------|

|               | E  |          | ES | Extra Segment              |

| BIU registers |    | CS<br>SS |    | Code Segment               |

|               |    |          |    | Stack Segment              |

|               |    | DS       |    | Data Segment               |

|               |    | IP       |    | Instruction Pointer        |

|               |    |          |    |                            |

|               | AX | AH       | AL | Accumulator                |

|               | BX | BH       | BL | Base Register              |

|               | CX | CH       | CL | Count Register             |

|               | DX | DH       | DL | Data Register              |

|               |    | SP       |    | Stack Pointer              |

|               |    | BP       |    | Base Pointer               |

|               |    | SI       |    | Source Index Register      |

| EU registers  |    | DI       |    | Destination Index Register |

|               |    | FLAGS    |    |                            |

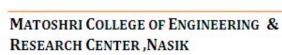

# 8086 Addressing Modes

#### 8086 Addressing Modes

- Register Addressing Mode

- 2. Immediate Addressing Mode

- 3. Memory Addressing Mode

- 4. String Addressing Mode

- 5. I/O Addressing Mode

- Implied Addressing Mode

#### 8086 Addressing Modes

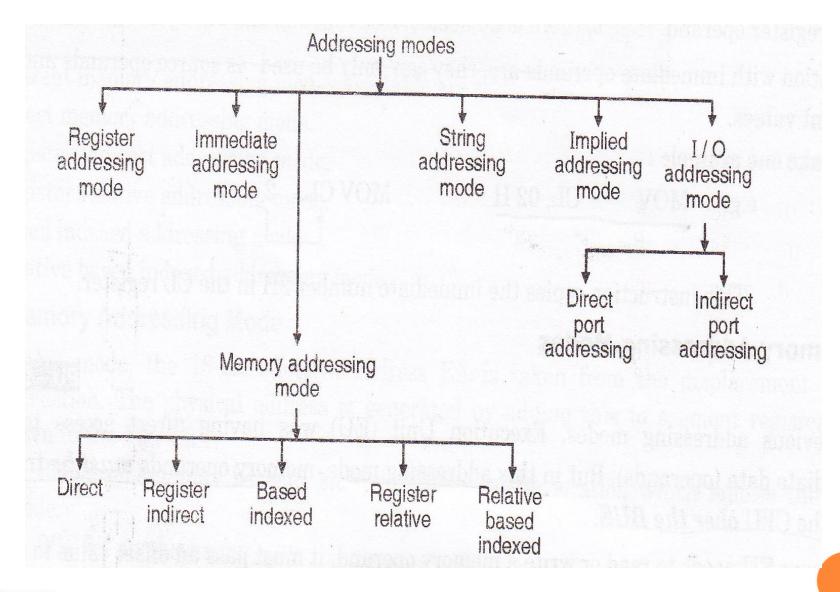

# 1.Register Addressing Mode

# Register Addressing Mode

- Data is in register and Instruction Specifies the perticular register

- E.g

MOV AX, BX

# 2.Immediate Addressing Mode

# 2. IMMEDIATE ADDRESSING MODE

- Immediate operand is Constant data contained in an Instruction

- i.e. The source operand is a part of instruction instade of register memory

- E.g.

MOV CL,02H

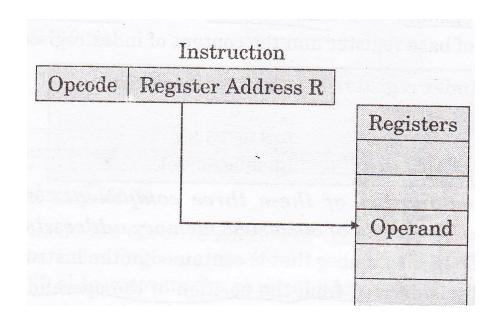

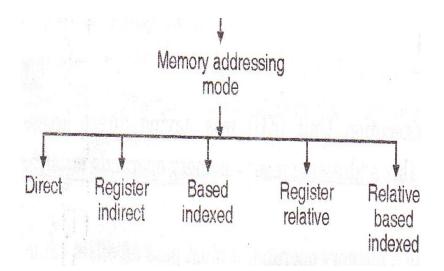

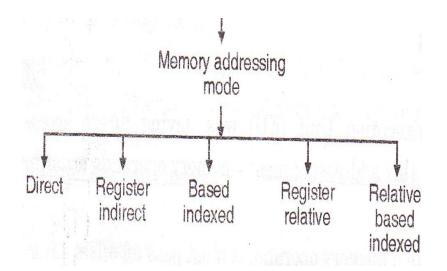

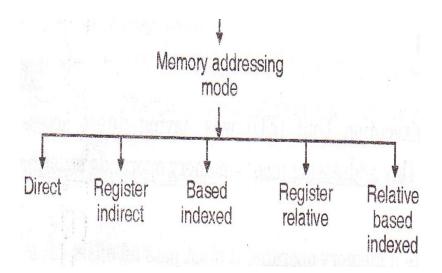

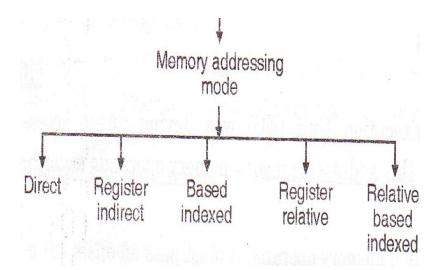

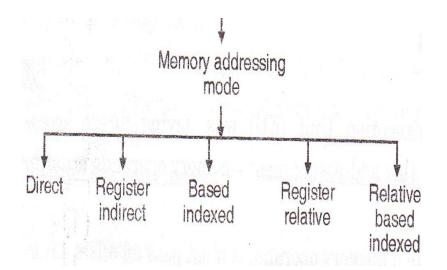

- 3.1 Direct

- 3.2 Register Indirect

- 3.3 Based Indexed

- 3.4 Register Relative

- 3.5 Relative Based Indexed

# **EFFECTIVE ADDRESS**

- The offset of a memory operand is called the operand's effective address (EA).

- Is an unsiged 16 bit no. That expresses the operands distance in byte from the begining of the segment

- 8086 has Base register and Index register

- So EU calculates EA by summing a Displacement, Content of Base register and Content of Index register.

- Displacement is an 8 or 16 bit no

- It is generally derived from the position of operand name.

- It's value is constant.

- Pogrammer may specify either BX or BP is to be used as Base Register

- Similarly either SI od DI may be specified as Index Register

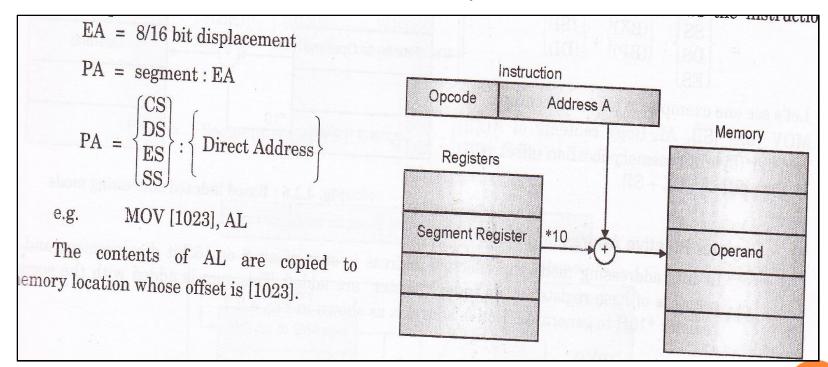

# 3.1 DIRECT MEMORY ADDRESSING MODE

- EA is taken from the displacement field of instruction.

- PA=This addr. Is added with Seg.Regi\*10 H

MOV[1023], AL

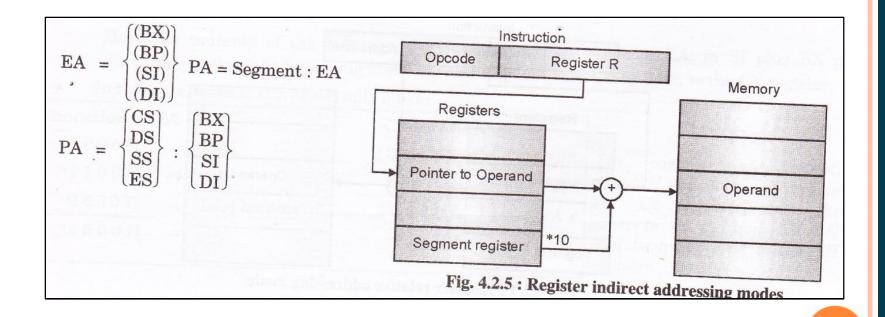

# 3.2 REGISTER INDIRECT ADDRESSING MODE

- EA of may be taken directly from *one of the base* register or index register.

- PA=This addr. Is added with Seg.Regi\*10 H

MOV[SI], AL

# 3.3 BASED INDEXED ADDRESSING MODE

- EA is sum of Base register and Index register.

- Both of which are specified by the instruction

- PA=This addr. Is added with Seg.Regi\*10 H

MOV[BX+SI], AL

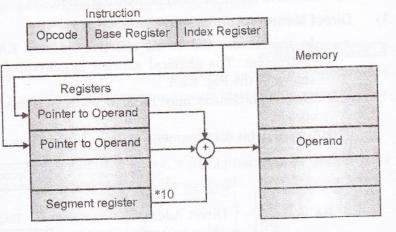

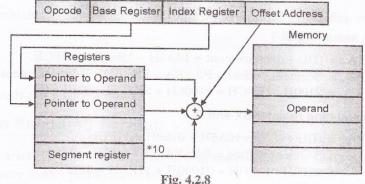

#### 3) Based Indexed Addressing Mode

• In this addressing mode, the EA is sum of a base register and an index register, both of which are specified by the instruction. The sum is added to the segment register \* 10 H to give effective address as shown in Fig. 4.2.6.

$$\therefore EA = \{Base register\} + \{Index register\}$$

$$= \begin{cases} (BX) \\ (BP) \end{cases} + \begin{cases} (SI) \\ (DI) \end{cases}$$

PA = Segment register : EA

$$=\begin{cases} CS \\ SS \\ DS \\ ES \end{cases} : \begin{cases} (BX) \\ (BP) \end{cases} + \begin{cases} (SI) \\ (DI) \end{cases}$$

Let's see one example, to clear the concept. MOV [BX] [SI], AL Copy contents of AL register (byte) to memory location offset is in [BX] [SI] i.e. [BX + SI].

Fig. 4.2.6: Based indexed addressing mode

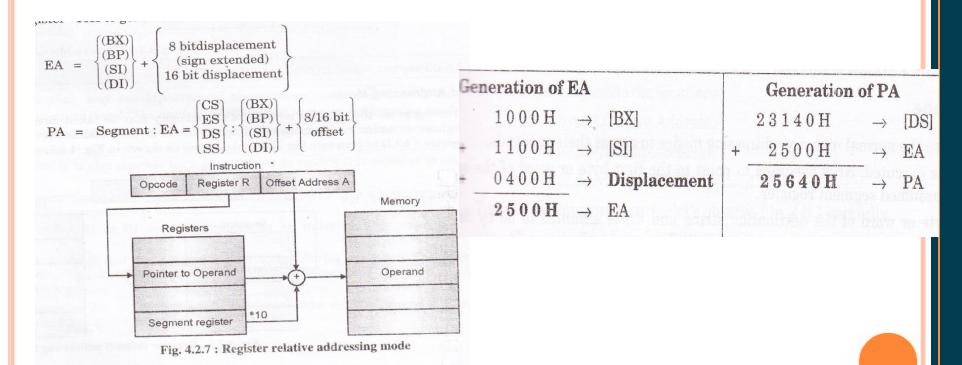

# 3.4 REGISTER RELATIVE ADDRESSING MODE

- EA is Sum of 8 or 16 bit displacement and contents of base register or an index register

- PA=This addr. Is added with Seg.Regi\*10 H

MOV[BX+1100], AL

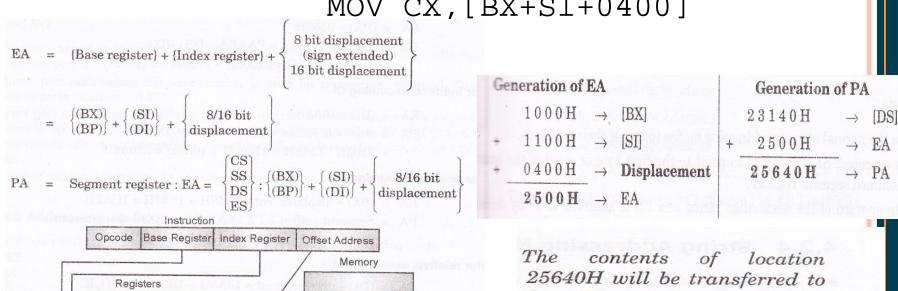

# 3.5 RELATIVE BASED INDEXED MODE

- EA is Sum of a Base register, an Index Register and Displacement.

- PA=This addr. Is added with Seg.Regi\*10 H

MOV CX, [BX+SI+0400]

The contents of location 25640H will be transferred to the CL register and the contents of location 25641H will be transferred to the CH register.